이전 글에서는 단일 사이클을 가정하고 데이터 패스를 설계했다.

[컴퓨터구조] Processor(2): 데이터패스 만들기

[컴퓨터구조] Processor(2): 데이터패스 만들기

먼저 데이터패스를 설계해보자. 이것을 시작하기 위해 RISC-V 명령어 종류 각각을 실행하는 데 필요한 주요 구성 요소들을 살펴본다.첫 번째 구성 요소는 instruction memory이다. 프로그램의 명령어를

turtle2.tistory.com

이번에는 파이프라인 단계를 고려해 설계해보자.

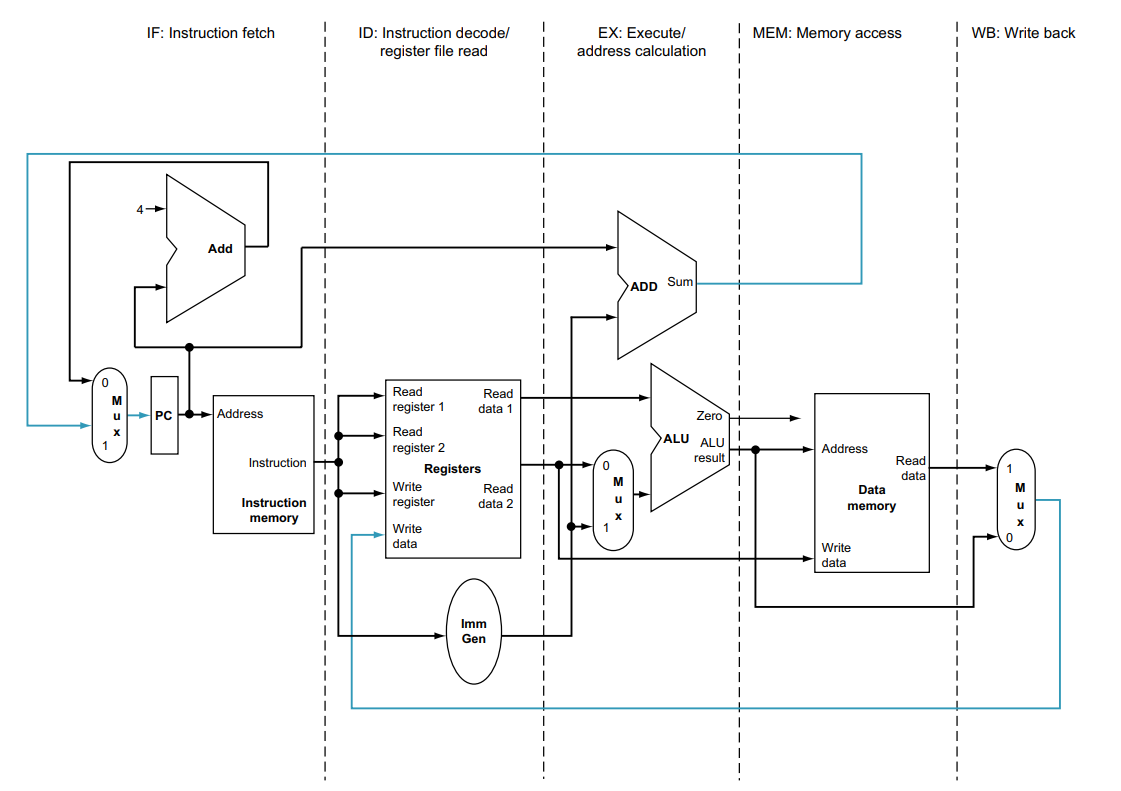

위 그림은 앞서 설계한 단일 사이클 데이터패스에 파이프라인 단계를 보여주고 있다. 각 부분은 명령어 실행 단계에 따라 이름이 붙여진다.

- IF: 명령어 인출

- ID: 명령어 해독 및 레지스터 파일 읽기

- EX: 실행 or 주소 계산

- MEM: 데이터 메모리 접근

- WB(write back): 쓰기

기본적으로 명령어와 데이터는 왼쪽에서 오른쪽으로 지나가며 실행된다. 하지만 두 가지 예외가 있는데, 하나는 쓰기 단계에서 결과를 데이터패스 중앙의 레지스터 파일로 보내는 것이고, 다른 하나는 증가된 PC값과 MEM 단계의 분기 주소 중 고르는 것이다.

이렇게 거꾸로 흐르는 데이터는 현재 명령어에는 영향을 주지 않고 파이프라인 뒤쪽에 있는 명령어들에만 영향을 미친다. 앞서 설명한 역순행 데이터 흐름 중 전자는 데이터 해저드를 일으킬 수 있고, 후자는 제어 해저드를 일으킬 수 있다.

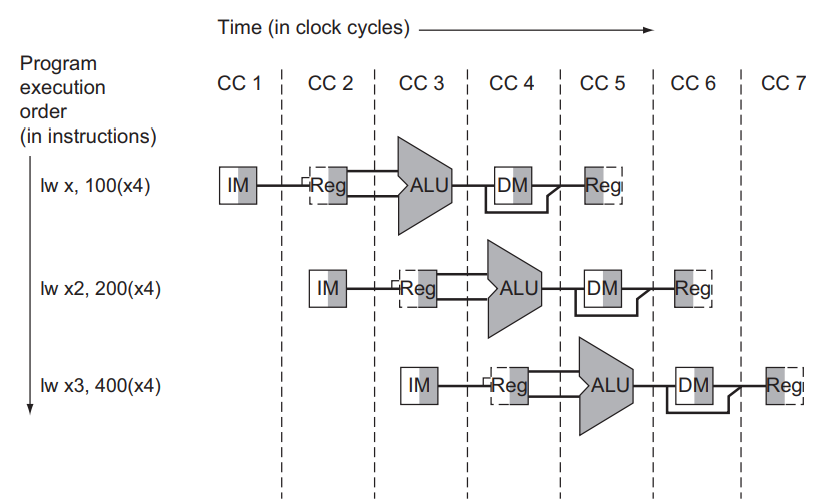

파이프라인 실행에서 일어나는 일을 시간 축에 배치해 살펴보자. 이와 같이 그리는 그림을 다중 클럭 사이클 파이프라인 다이어그램(multiple clock cycle pipeline diagrams)이라고 부른다.

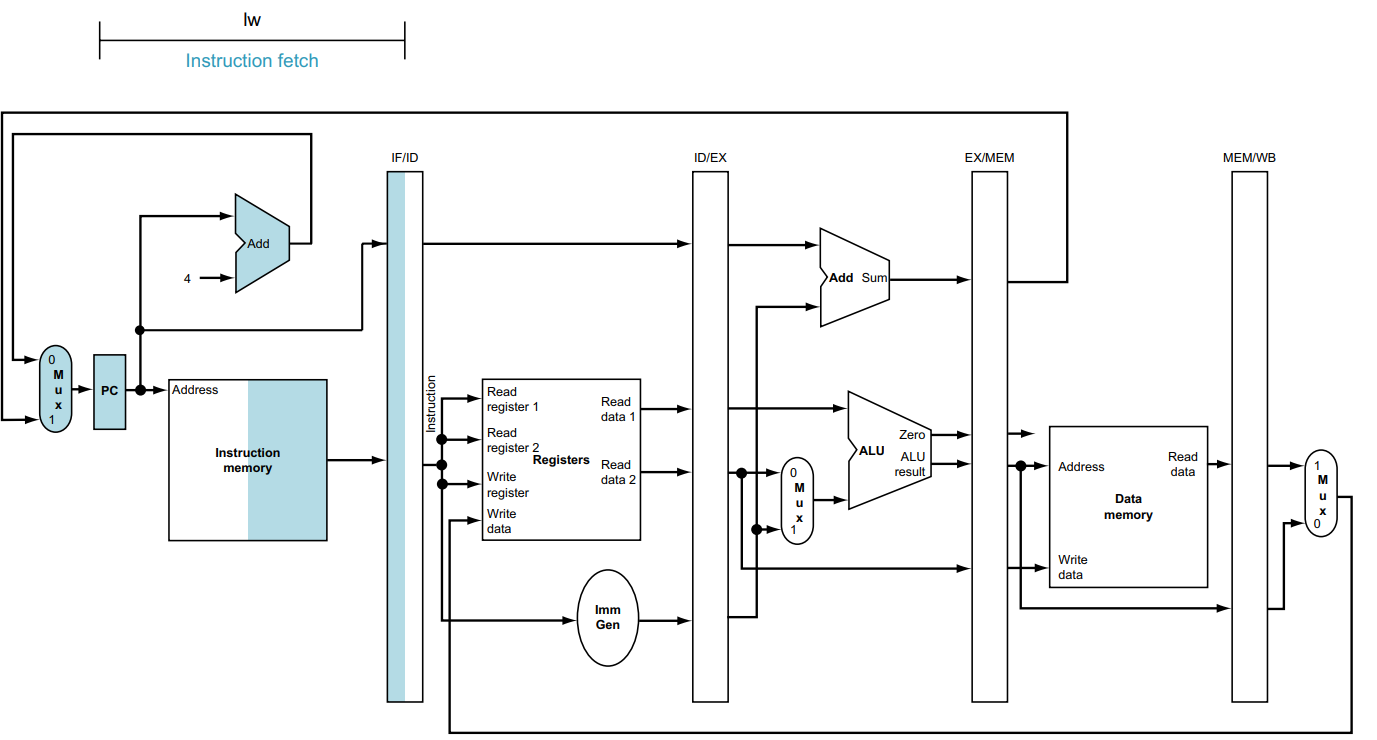

이와 같은 실행이 가능하게 하기 위해 데이터를 유지하는 레지스터를 추가해 한 데이터패스의 부분부분이 공유될 수 있게 한다. 아래와 같은 그림은 단일 클럭 사이클 파이프라인 다이어그램(single clock cycle pipieline diagrams)이라고 부른다.

파이프라인 레지스터의 이름은 이 레지스터가 분리하고 있는 두 단계의 이름을 따서 붙여진다. WB 단계 뒤에는 파이프라인 레지스터가 없다는 것을 확인하자. 어떤 프로세서의 상태를 갱신하는 과정은 별도의 파이프라인 레지스터가 필요하지 않다.

우선 해저드를 생각하지 않고 파이프라이닝 과정에 대해 살펴보자.

1. 적재 명령어 (lw)

적재 명령어에서는 다섯 단계 모두에서 활성화된다.

- Instruction fetch (IF): PC에 있는 주소를 사용해 메모리에서 명령어 읽어오고, IF/ID 파이프라인 레지스터에 저장한다. PC 주소는 4만큼 증가되어 PC에 다시 저장된다. PC은 beq 명령어의 경우 나중에 사용될 수 있기에 파이프라인 레지스터에도 저장된다.

- Instruction decode and register file read (ID): IF/ID 파이프라인 레지스터의 명령어 부분에서 수치 필드와 읽어야할 레지스터 번호 2개를 제공한다. 세 값 모두 PC 주소값과 함께 ID/EX 파이프라인 레지스터에 저장된다(rd 필드에서 목적지 레지스터 번호를 함께 저장한다).

- Execute or address calculation (EX): 한 레지스터의 내용과 부호확장된 수치값을 읽고 ALU를 사용해 둘을 더한 합을 EX/MEM 파이프라인 레지스터에 저장한다.

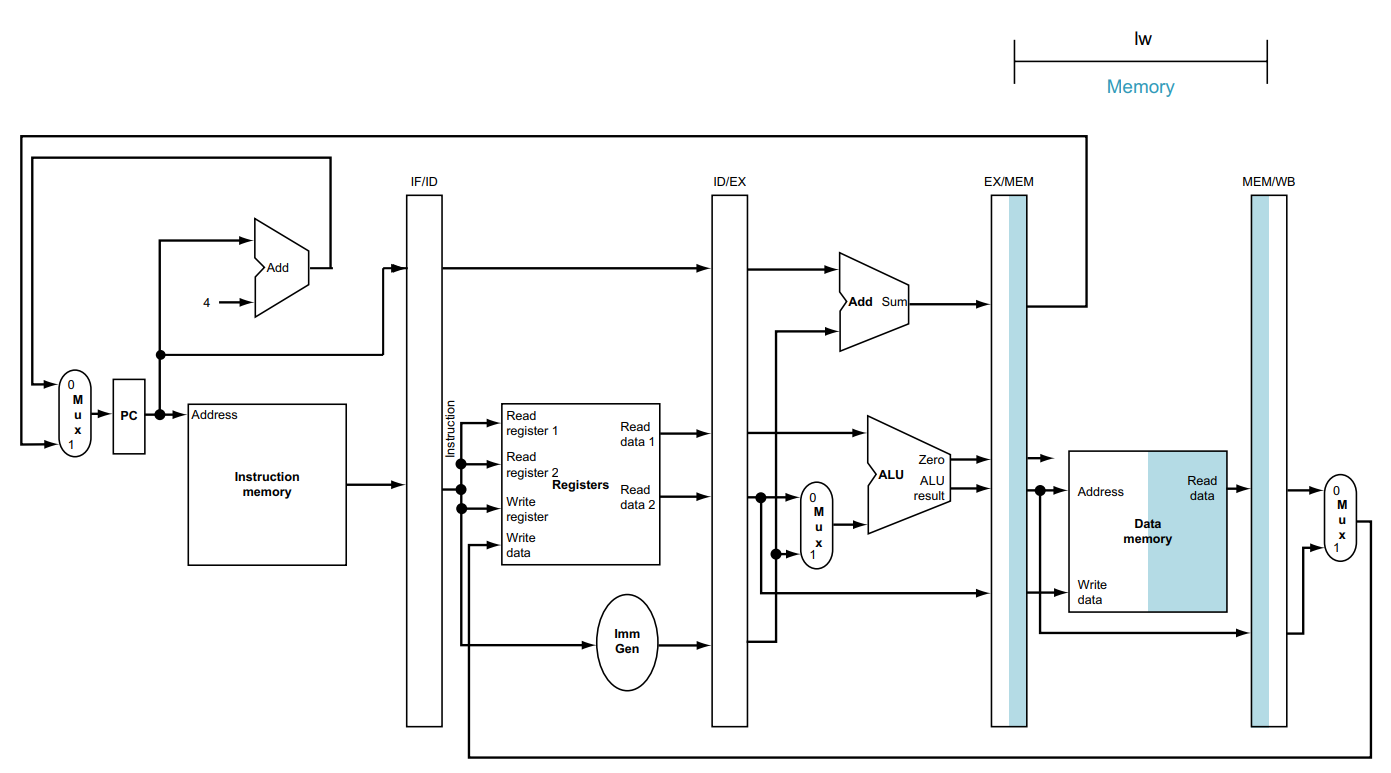

- Memory access (MEM): EX/MEM 파이프라인 레지스터에서 주소를 받아 데이터 메모리를 읽고 이 데이터를 MEM/WB 파이프라인 레지스터에 저장한다.

- Write-back (WB): MEM/WB 파이프라인 레지스터를 읽어 그 데이터를 그림 중앙에 있는 레지스터 파일에 쓴다.

사실 굵은 글씨로 표시한 부분 또한 구현에 추가해야한다. 해당 부분을 추가한 그림을 소개한다.

2. 저장 명령어 (sw)

적재 명령어와 과정이 유사하다.

- Instruction fetch (IF)

- Instruction decode and register file read (ID): 처음 두 단계는 모든 명령어가 동일하다. 아직 명령어 종류를 알 수 없기 때문이다. (다만, 저장 명령어의 경우 적재 명령어와는 달리 두 번째 레지스터를 읽기 위해 rs2 필드를 사용한다.)

- Execute or address calculation (EX): 적재 명령어와 동일

- Memory access (MEM): EX/MEM 파이프라인 레지스터에 저장되어 있는 rs2 필드 레지스터의 값을 메모리에 쓴다.

- Write-back (WB): 아무런 일도 일어나지 않는다. 하지만 뒤따르는 명령어들이 있기 때문에 아무런 일을 하지 않아도 단계를 거쳐 가야 한다.

저장 명령어에서 특이적인 4번 과정만 그림으로 보여주겠다.

적재 명령어와 저장 명령어는 또 다른 중요한 점을 보여준다. 데이터 패스의 각 구성요소들이 한 파이프라인 단계에서만 사용될 수 있다는 것이다. 즉, 명령어 메모리, 레지스터 읽기 포트, ALU, 데이터 메모리, 레지스터 쓰기 포트 등을 여러 단계에서 동시에 사용할 수 없다. 그렇지 않으면 structural hazard가 발생한다.

다음 글에서는 파이프라인 데이터패스에 제어를 추가해보도록 하겠다.

'Computer > 컴퓨터구조' 카테고리의 다른 글

| [컴퓨터구조] Pipelining(4): 데이터 해저드 (Data Hazard) (0) | 2024.06.02 |

|---|---|

| [컴퓨터구조] Pipelining(3): 파이프라인 제어 (0) | 2024.06.01 |

| [컴퓨터구조] Pipelining(1): 파이프라이닝이란 (0) | 2024.06.01 |

| [컴퓨터구조] Processor(3): 제어 유닛 (control unit) (0) | 2024.06.01 |